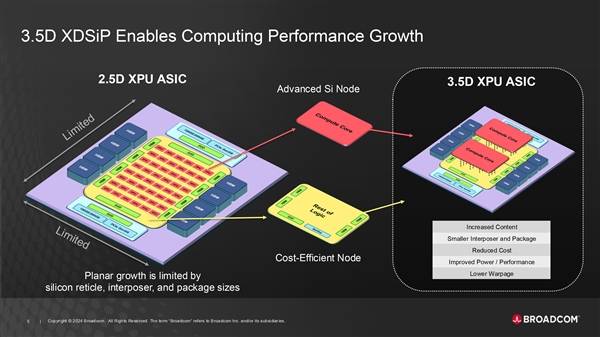

博通公司近日发布了其革命性的3.5D XDSiP封装技术,该技术专为高性能AI和HPC处理器打造,旨在应对不断增长的计算能力需求。该封装平台能够支持的最大芯片面积达到惊人的6000平方毫米。

为了更形象地展示这一面积,我们可以将其与NVIDIA即将推出的Blackwell架构旗舰芯片GB202相比较。GB202的芯片面积仅为744平方毫米,而博通的3.5D XDSiP平台支持的芯片面积,相当于大约八块GB202芯片的总面积。

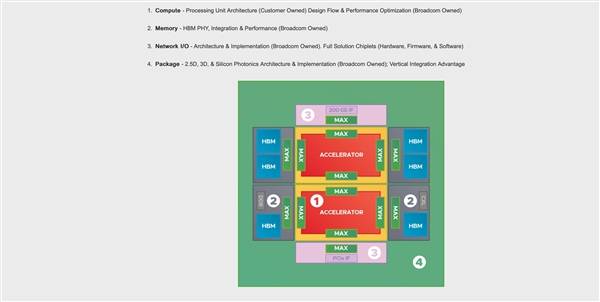

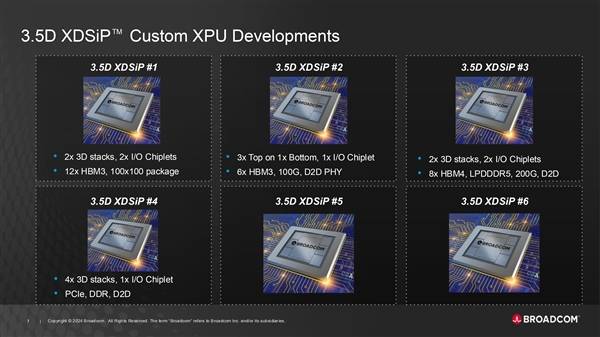

在技术层面,博通的3.5D XDSiP平台结合了台积电的CoWoS-L封装技术和2.5D集成、3D封装的优势,因此得名3.5D。该平台能够将3D堆叠芯片、网络与I/O芯粒以及HBM内存高效整合,形成系统级封装(SiP)。其最大中介层面积可达4719平方毫米,是光罩面积的5.5倍,并且支持最多12颗HBM3或HBM4高带宽内存芯片的封装。

为了追求极致性能,博通采用了F2F(面对面)方法,利用混合铜键合(HCB)技术,实现不同计算芯粒的堆叠。这种方案的关键在于,采用无凸起HCB技术直接堆叠上层和底层芯片,省去了传统的TSV硅通孔。

这种创新技术带来了显著优势:信号连接数量提升了约7倍,信号传输路径缩短,互连功耗最高可降低90%,大幅降低了延迟,同时提供了更高的堆叠灵活性。

博通计划利用这一先进封装平台,为Google、Meta、OpenAI等科技巨头定制AI/HPC处理器和ASIC芯片。此外,博通还将提供丰富的IP资源,包括HBM PHY、PCIe、GbE,甚至是全套芯粒方案和硅光子技术。这使客户可以专注于处理器核心部分——处理单元架构的设计,无需担心外围IP和封装问题。

据博通透露,首款基于3.5D XDSiP封装平台的产品预计将在2026年面市,这将为AI和HPC领域带来一场技术革新。

暂无评论